# FOR MORE EXCLUSIVE

# (Civil, Mechanical, EEE, ECE)

# **ENGINEERING & GENERAL STUDIES**

## (Competitive Exams)

# TEXT BOOKS, IES GATE PSU's TANCET & GOVT EXAMS Notes & Anna University Study Materials

# VISIT

# www.EasyEngineering.net

AN EXCLUSIVE WEBSITE FOR ENGINEERING STUDENTS & GRADUATES

**\*\*Note:** Other Websites/Blogs Owners Please do not Copy (or) Republish this Materials without Legal Permission of the Publishers.

**\*\*Disclimers :** EasyEngineering not the original publisher of this Book/Material on net. This e-book/Material has been collected from other sources of net.

Downloaded From : www.EasyEngineering.net

### EC6009 ADVANCED COMPUTER ARCHITECTURE LTPC 3003 UNIT I FUNDAMENTALS OF COMPUTER DESIGN 9 Review of Fundamentals of CPU, Memory and IO – Trends in technology, power, energy and cost, Dependability - Performance Evaluation UNIT II INSTRUCTION LEVEL PARALLELISM 9 ILP concepts - Pipelining overview - Compiler Techniques for Exposing ILP -Dynamic Branch Prediction – Dynamic Scheduling – Multiple instruction Issue – Hardware Based Speculation - Static scheduling - Multi-threading - Limitations of ILP – Case Studies.

### UNIT III DATA-LEVEL PARALLELISM

Vector architecture – SIMD extensions – Graphics Processing units – Loop level parallelism.

### UNIT IV THREAD LEVEL PARALLELISM

Symmetric and Distributed Shared Memory Architectures – Performance Issues – Synchronization – Models of Memory Consistency – Case studies: Intel i7 Processor, SMT & CMP Processors.

### UNIT V MEMORY AND I/O

Cache Performance – Reducing Cache Miss Penalty and Miss Rate – Reducing Hit Time – Main Memory and Performance – Memory Technology. Types of Storage Devices – Buses – RAID – Reliability, Availability and Dependability – I/O Performance Measures.

### TOTAL: 45 PERIODS

9

9

9

### **TEXT BOOK:**

1. John L Hennessey and David A Patterson, "Computer Architecture A Quantitative Approach", Morgan Kaufmann/ Elsevier, Fifth Edition, 2012.

### **REFERENCES:**

1. Kai Hwang and Faye Briggs, "Computer Architecture and Parallel Processing", Mc Graw-Hill International Edition, 2000.

2. Sima D, Fountain T and Kacsuk P, "Advanced Computer Architectures: A Design Space Approach", Addison Wesley, 2000.

### EC 6009 ADVANCED COMPUTER ARCHITECTURE

### 1. Aim and Objective of the subject

- Understand the micro-architectural design of processors

- Learn about the various techniques used to obtain performance improvement and power savings in current processors

- To familiarize the students with Instruction Level Parallelism and Data-Level Parallelism

- To expose the students to the concept of Thread Level Parallelism

- To familiarize the students with Memory and I/O

### 2. Need and Importance for the study of the subject

- Evaluate performance of different processor architectures with respect to various parameters

- Analyze performance of different Instruction Level Parallelism techniques

- Evaluate performance of Data-Level Parallelism andThread Level

Parallelism

- Identify cache and memory related issues in multi-processors

### 3. Industry Connectivity and Latest Developments

- Latest processor's architecture in computers (SMT, CMP, Intel i7 Processor's) are analyzed.

- VLIW and Vector architectures play a vital role in industries

- 4. Industry Visit (Planned if any) --NIL---

### **TEXT BOOK:**

1. John L Hennessey and David A Patterson, "Computer Architecture A Quantitative Approach", Morgan Kaufmann/ Elsevier, Fifth Edition, 2012. **REFERENCES:**

1. Kai Hwang and Faye Briggs, "Computer Architecture and Parallel Processing", Mc Graw-Hill International Edition, 2000.

2. Sima D, Fountain T and Kacsuk P, "Advanced Computer Architectures: A Design Space Approach", Addison Wesley, 2000.

4

| Si.<br>No |    | Topics to be covered                                                               | Hours<br>required /<br>planned | Cumulative<br>Hrs | Books<br>Referred | Page<br>No.            |  |  |

|-----------|----|------------------------------------------------------------------------------------|--------------------------------|-------------------|-------------------|------------------------|--|--|

|           |    | UNITI FUNDAMENTALS OF COMPUTER DESIGN                                              |                                |                   |                   |                        |  |  |

| 1         | I  | Review of Fundamentals of CPU,<br>Memory, IO                                       | 3                              | 3                 | T1                | 2-17                   |  |  |

| 2         |    | Trends in technology Instructions                                                  | 1                              | 4                 | T1                | 17-21                  |  |  |

| 3         |    | Power, Energy                                                                      | 2                              | 6                 | T1                | 21-26                  |  |  |

| 4         |    | Cost                                                                               | 1                              | 7                 | T1                | 27-33                  |  |  |

| 5         |    | Dependability                                                                      | 1                              | 8                 | T1                | 33-36                  |  |  |

| 6         |    | Performance Evaluation                                                             | 1                              | 9                 | T1                | 36-44                  |  |  |

|           |    | UNITII INSTRUCTION LEVEL PARALLELISM                                               |                                |                   |                   |                        |  |  |

| 7         |    | ILP concepts, Pipelining overview                                                  | 1                              | 10                | T1                | 148-156                |  |  |

| 8         |    | Compiler Techniques for Exposing ILP                                               | 2                              | 12                | T1                | 156-162                |  |  |

| 9         |    | Dynamic Branch Prediction                                                          | 1                              | 13                | T1                | 162-167                |  |  |

| 10        |    | Dynamic Scheduling                                                                 | 1                              | 14                | T1                | 167-183                |  |  |

| 11        |    | Hardware Based Speculation                                                         | 1                              | 15                | T1                | 183-192                |  |  |

| 12        |    | Multiple instruction Issue - Static                                                | 1                              | 16                | T1                | 192-202                |  |  |

| 13        |    | Multi-threading                                                                    | 1                              | 17                | T1                | 223-232                |  |  |

| 14        |    | Limitations of ILP                                                                 | 1                              | 18                | T1                | 213-221                |  |  |

| 15        |    | Case Studies                                                                       | 1                              | 19                | T1                | 247-254                |  |  |

|           |    | UNIT III DATA-LEVEI                                                                | L PARAL1                       |                   |                   |                        |  |  |

| 16        |    | Vector architecture                                                                | 2                              | 21                | T1                | 264-282                |  |  |

| 17        |    | SIMD extensions                                                                    | 3                              | 24                | T1                | 282-288                |  |  |

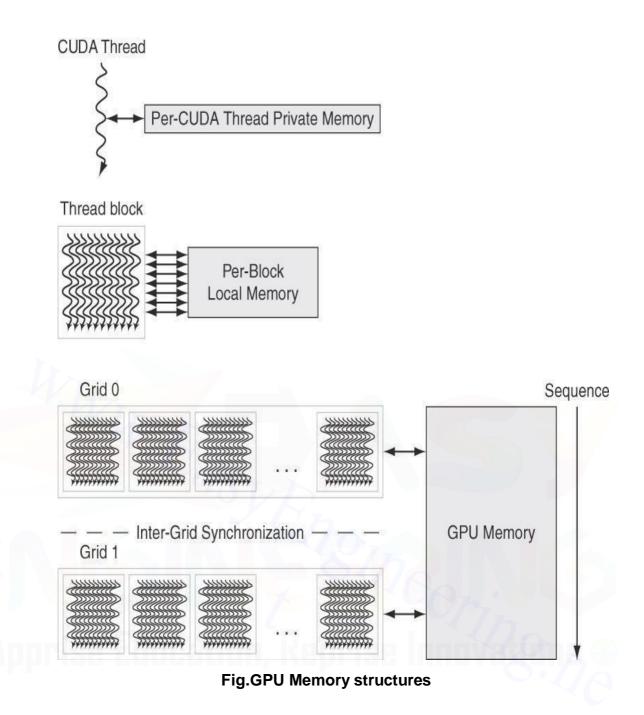

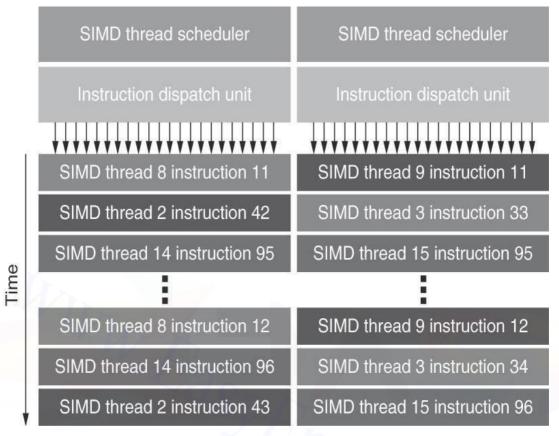

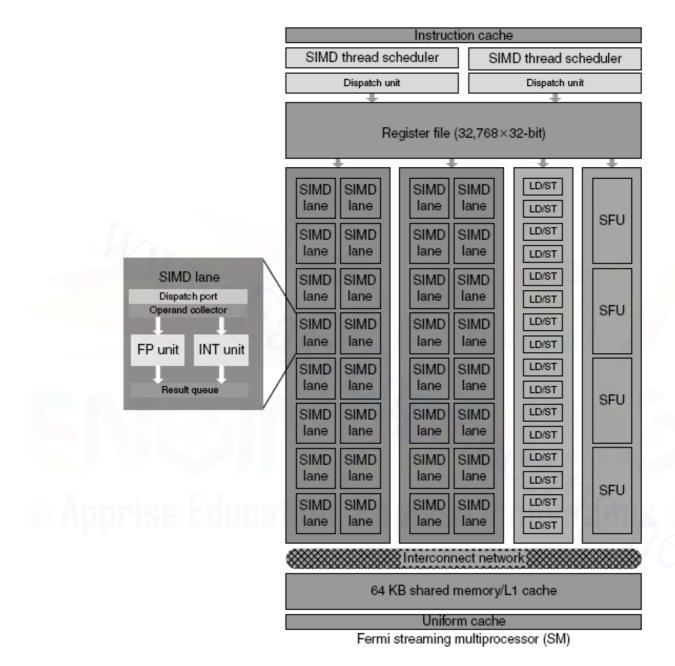

| 18        |    | Graphics Processing units                                                          | 2                              | 26                | T1                | 288-315                |  |  |

| 19        |    | Loop level parallelism                                                             | 2                              | 28                | T1                | 315-322                |  |  |

|           | 2  | UNITIV THREAD LEV                                                                  | EL PARAL                       | LELISM            |                   |                        |  |  |

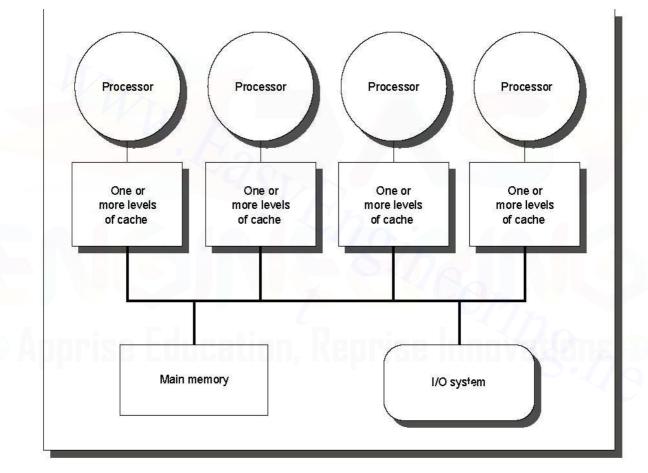

| 20        |    | Symmetric Shared Memory<br>Architectures                                           | 2                              | 30                | T1                | 366-378                |  |  |

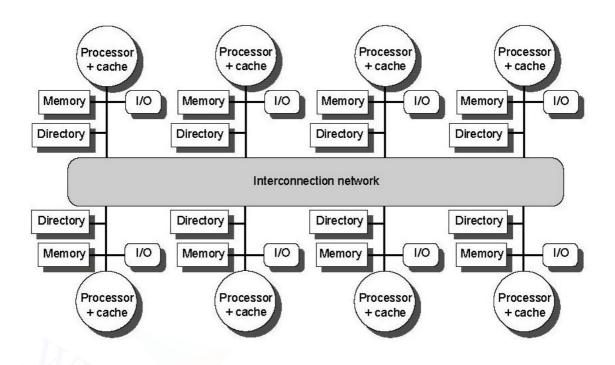

| 21        |    | Distributed Shared Memory<br>Architectures                                         | 2                              | 32                | T1                | 3 <mark>78</mark> -386 |  |  |

| 22        |    | Performance Issues                                                                 | 1                              | 33                | T1                | 395-400                |  |  |

| 23        | IV | Synchronization                                                                    | 1                              | 34                | T1                | 386-391                |  |  |

| 24        | IV | Models of Memory Consistency                                                       | 1                              | 35                | T1                | 392-395                |  |  |

| 25        |    | Case studies: Intel i7 Processor, SMT<br>Processor, CMP Processor                  | 2                              | 37                | T1                | 401-405                |  |  |

|           |    | UNITV MEMO                                                                         | RY ANDI/C                      | )                 |                   | Y Y                    |  |  |

| 26        |    | Cache Performance- Reducing Cache<br>Miss Penalty, Miss Rate, Reducing Hit<br>Time | 3                              | 40                | T1                | 78-96                  |  |  |

| 27        | V  | Main Memory and Performance                                                        | 1                              | 41                | T1                | 72-78                  |  |  |

|           |    | Memory Technology                                                                  | 1                              | 42                | T1                | 96-105                 |  |  |

| 29        |    | Types of Storage Devices                                                           | 1                              | 43                | T1                | D12-35                 |  |  |

| 30        |    | Buses                                                                              | 1                              | 44                | T1                | 116                    |  |  |

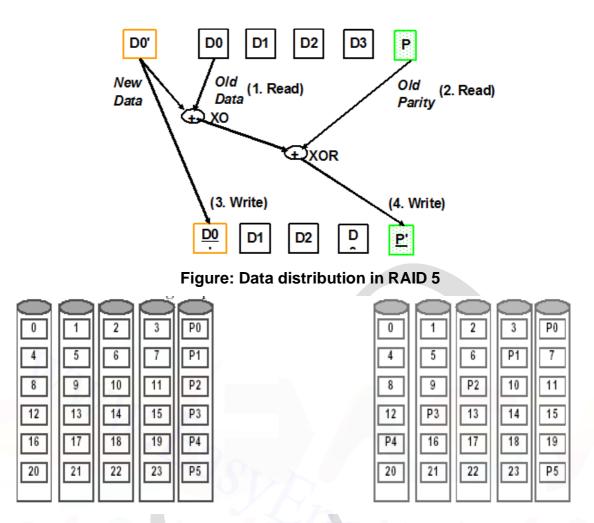

| 31        | V  | RAID – Reliability, Availability and<br>Dependability                              | 1                              | 45                | T1                | D44-59                 |  |  |

| 32        | V  | I/O Performance Measures                                                           | 1                              | 46                | T1                | D15-16                 |  |  |

| 52        | v  |                                                                                    | •                              | 10                | • •               | 21010                  |  |  |

Total: 46 Hours

| UNIT | Q. No          | TITLE                                                            | Page N   |  |  |  |

|------|----------------|------------------------------------------------------------------|----------|--|--|--|

|      | 1-15           | Part A                                                           | 7-10     |  |  |  |

|      |                | Part B                                                           |          |  |  |  |

|      | 1              | Components of a computer system                                  | 11       |  |  |  |

|      | 0              | CPU performance equation and factors that affect the performance | 45       |  |  |  |

|      | 2              | of a computer                                                    | 15       |  |  |  |

|      | 3 (i)          | Uniprocessors, multiprocessors and performance chart             | 18       |  |  |  |

| I    | 3 (ii)         | Power wall                                                       | 19       |  |  |  |

|      | 3 (iii)        | Fundamentals of computer Design                                  |          |  |  |  |

|      | 4 (i)          | Technology trends in computer industry                           |          |  |  |  |

|      | 4 (ii)         | Trends in Cost, Price for building computer over time            |          |  |  |  |

|      | 5 (i)          | Design alternatives using the CPU performance equation           | 23<br>25 |  |  |  |

|      | 5 (ii)         | Clock rate target for a best design                              | 26       |  |  |  |

|      | 1-15           | Part A                                                           | 27-29    |  |  |  |

|      |                | Part B                                                           |          |  |  |  |

|      | 1 (i)          | Multithreading                                                   | 30       |  |  |  |

|      | 1 (ii)         | Comparison of hardware and software speculation mechanisms       | 33       |  |  |  |

|      | 2              | Hardware based speculation to overcome the control dependencies  | 33       |  |  |  |

| II C | 3 (i)          | Compiler techniques for exploiting Instruction Level Parallelism | 37       |  |  |  |

|      | 3 (ii)         | Explain the various dynamic branch prediction schemes            | 39       |  |  |  |

|      | 3 (ll)<br>4    | Dynamic Scheduling, Tomosulo's approach.                         | 43       |  |  |  |

|      | 5 (i)          | Concept of ILP with dependencies in ILP.                         |          |  |  |  |

|      |                | Limitations of ILP                                               | 49<br>52 |  |  |  |

|      | 5 (ii)<br>1-15 | Part A                                                           | 54-5     |  |  |  |

|      | 1-15           |                                                                  | 54-50    |  |  |  |

|      | 1              | Part B                                                           | 57       |  |  |  |

|      | 1              | Loop Level Parallelism?                                          | 57<br>64 |  |  |  |

|      | 2              | SIMD extensions exploit data-level parallelism                   |          |  |  |  |

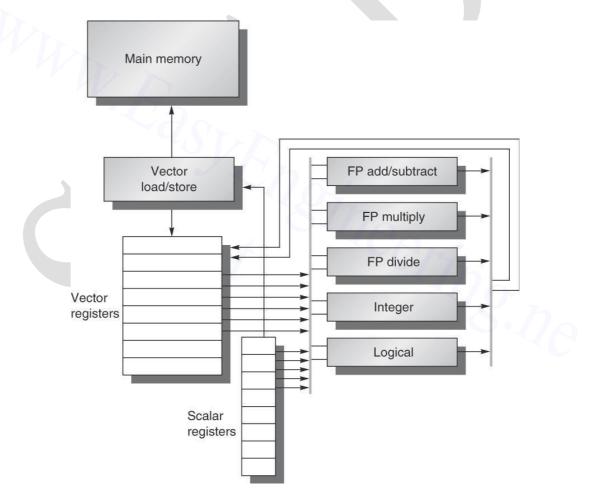

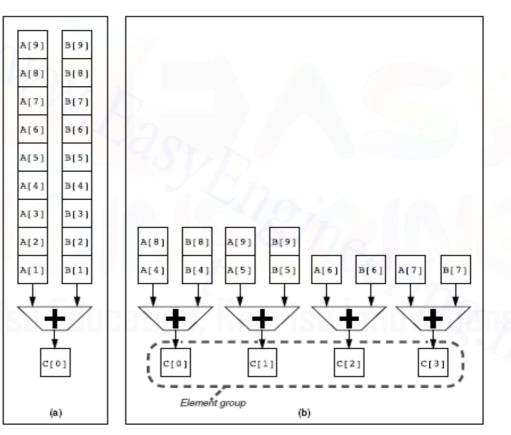

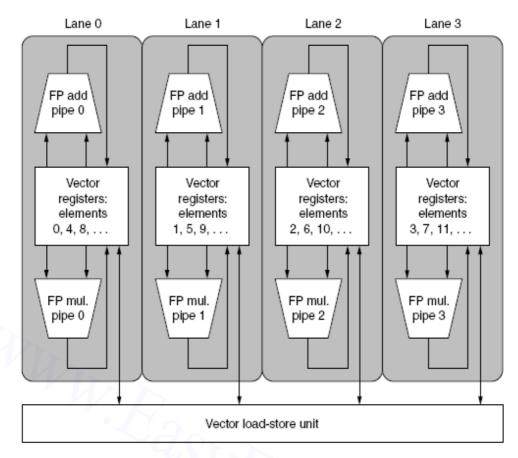

| III  | 3              | Vector Architectures of data-level parallelism.                  |          |  |  |  |

|      | 4              | Graphics Processing Units and its Programming                    | 75       |  |  |  |

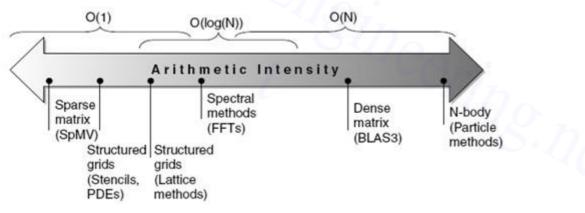

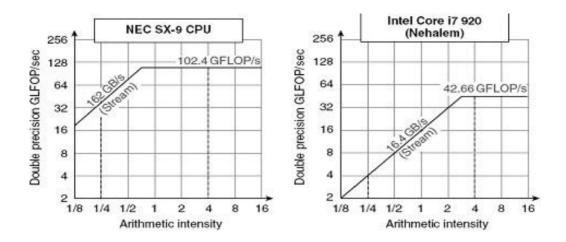

|      | 5 (i)          | Arithmetic intensity of kernel, Convert loop into VMIPS assembly |          |  |  |  |

|      |                | code                                                             | 84       |  |  |  |

|      | 5 (ii)         | Detection and enhancement of Loop Level Parallelism              | 86       |  |  |  |

|      | 1-15           | Part A                                                           | 90-92    |  |  |  |

|      |                | Part B                                                           |          |  |  |  |

|      | 1              | Symmetric shared memory architecture.                            | 93       |  |  |  |

| IV   | 2              | Distributed shared memory, NUMA architecture                     | 97       |  |  |  |

|      | 3              | Synchronization process used in multiprocessor system            | 102      |  |  |  |

|      | 4              | Needs and types of memory consistency models                     | 105      |  |  |  |

|      | 5              | CMP and SMT architecture and its performance                     | 108      |  |  |  |

|      | 1-15           | Part A                                                           | 113-     |  |  |  |

|      | 1-13           |                                                                  | 115      |  |  |  |

|      |                | Part B                                                           |          |  |  |  |

|      | 1              | Cache optimization scheme.                                       | 116      |  |  |  |

| V    | 2 (i)          | Hit time reduction techniques to improve cache performance       | 124      |  |  |  |

|      | 2 (ii)         | Methods to measure the performance of I/O                        | 128      |  |  |  |

|      | 3              | Main memory performance?                                         | 130      |  |  |  |

|      | 4              | RAID architecture                                                | 137      |  |  |  |

|      | 5              | Types of storage devices.                                        | 145      |  |  |  |

|      |                | Previous University Question Papers                              | 149-16   |  |  |  |

### DEPARTMENT OF ELECTRONICS & COMMUNICATION ENGINEERING EC6009 ADVANCED COMPUTER ARCHITECTURE QUESTION BANK

### UNIT I - FUNDAMENTALS OF COMPUTER DESIGN PART A

- 1. What are the five trends in computer Technology? (NOV/DEC 2016)

- Multi processors

- VLSI Technology Trends

- Advanced machine learning

- Internet of Things (IOT)

- Cloud computing

- 2. What are the components of a computer? [May/June 2014]

- Input unit

- Memory unit

- Arithmetic and Logic Unit

- Output unit

- Control unit

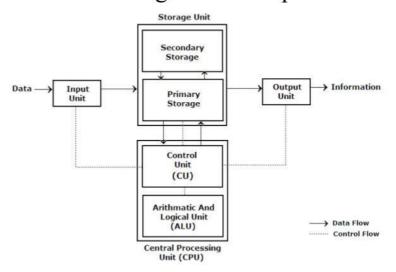

### 3. Draw the block diagram of computer. [R-2013]

### Block diagram of computer

### **Block Diagram of Computer**

### 1. What is Execution time/Response time??[May/June 2015]

Response time also called execution time. The total time required for the computer to complete a task, including disk accesses, memory accesses, I/O activities, operating system overhead, CPU execution time, and so on.

### 2. How to find the cost of an Integrated circuit ? (NOV/DEC 2016)

The cost of an integrated circuit varies between computers. In case of personal mobile devices increasing the performance of the whole system on chip (SOC), the cost of IC is greater than cost of PMD.

Cost of a packaged IC = ( cost of die + cost of testing die + cost of packing and final test ) / final test field.

# 4. What is CPU execution time, user CPU time and system CPU time and Write the expression for CPU time? ?[May/June 2014]

**CPU time**: The actual time the CPU spends computing for a specific task. **User CPU time**: The CPU time spent in a program itself.

**System CPU time**: The CPU time spent in the operating system performing tasks on behalf the program.

CPU time= CPU clock cycles for a program x Clock cycle time

or

CPU time= CPU clock cycles for a program / Clock rate

### 5. What is clock cycle and clock period? [R-2013]

Clock cycle: The time for one clock period, usually of the processor clock, this runs at a constant rate.

**Clock period**: The length of each clock cycle.

### 6. Define CPI and Write the expression for CPI time. [R-2013]

The term Clock Cycles Per Instruction Which is the average number of clock cycles each 3 instruction takes to execute, is often abbreviated as CPI. CPI time= CPU clock cycles for a program / Instruction count

### 7. State and explain the performance equation?[R-2013]

Suppose that the average number of basic steps needed to execute one machine instruction is S, where each basic step is completed in one clock cycle. If the clock cycle rate is R cycles per second, the processor time is given by  $T = (N \times S) / R$ . This is often referred to as the basic performance equation. Where N denotes number of machine Instructions.

### 8. Define MIPS and MIPS Rate.?[Nov/Dec 2014]

**MIPS:** Million Instructions Per Second (MIPS) is a measurement of program execution speed based on the number of millions of instructions. MIPS is computed

$MIPS = \frac{Instruction \ count}{Execution \ time \times 10^6}$

as:

This MIPS measurement is also called Native MIPS to distinguish it from some alternative definitions of MIPS.

**MIPS Rate**. The rate at which the instructions are executed at a given time.

### 9. Define Throughput and Throughput rate. [R-2013]

**Throughput** -The total amount of work done in a given time.

Throughput rate-The rate at which the total amount of work done at a given time.

### 10. Define Amdahl's law. [R-2013]

It States that performance improvement to be gained by using faster mode of execution limited by the fraction of time the faster mode can be used. Amdahl's

$law defines the term speedup which is given by, \\ Speedup = \frac{Performanceofentiretaskusingtheenhancementwhenpossible}{Performanceforentiretaskwithoutusingtheenhancement}$

$speedup = \frac{Execution time for entire task without using the enhancement}{Execution time of entire task using the enhancement when possible}$

Amdahl's law states that in parallelization, if P is the proportion of a system or program that can be made parallel, and 1-P is the proportion that remains serial, then the maximum speed up that can be achieved using N number of processors is 1/((1-P)+(P/N)).

11. Calculate speedup <sub>overall</sub> using Amdahl's law given that a new CPU, which is 10 times faster than the original CPU on computation, is additionally introduced. The original CPU is busy with computations 40% of time and I/O wait time is 60%.[R-2013]

Given: Fraction enhanced=0.4, Speedup enhanced=10

speedup<sub>overall</sub> =

$$\frac{1}{(1 - \text{Fraction}_{\text{enhanced}}) + \frac{\text{Fraction}_{\text{enhanwed}}}{\text{Speedup}_{\text{enhanwed}}}}$$

speedup =

$$\frac{1}{(0.6) + \frac{0.4}{10}} = 1.5625$$

### 12. What do you infer from the term dependability?(Apr/may 2017)

Computers not only need to be fast, they need to be dependable. Since any physical device can fail, the system must dependable by including redundant components that can take over when a failure occurs and to help to detect failures.

### 13. Find the number of dies per 30 cm wafer for a die that is 0.7 cm on a side. [R-2013]

Solution:

Total die area is 0.49cm<sup>2</sup>

Diesperwafer =

$$\frac{\pi x (\frac{30}{2})^2}{0.49} - \frac{\pi x 30}{\sqrt{2} x 0.49} = 1347$$

14. Find the yield for dies that are I cm on a side and 0.7 cm on a side, assuming a defect density of 0.6 cm2. [R-2013]

Solution:

Total die area is 0.49cm<sup>2</sup>

For larger die

*Dieyield* =

$$1 + (\frac{0.6x1}{4})^{-4} = 0.57$$

For smaller die  $Dieyield = 1 + (\frac{0.6x0.49}{4})^{-4} = 0.75$

### 15. What are the two main measures of dependability? [R-2013]

**Module reliability:** It is a measure of the continuous service accomplishment from a reference initial instant.

**Module Availability:** It is a measure of the service accomplishment with respect to the alternation between the two states of accomplishment and interruption.

# Apprise Education, Reprise Innovations

### PART B

# 1. Explain the Components of a computer system with the block diagram in detail.

### [R-2013]

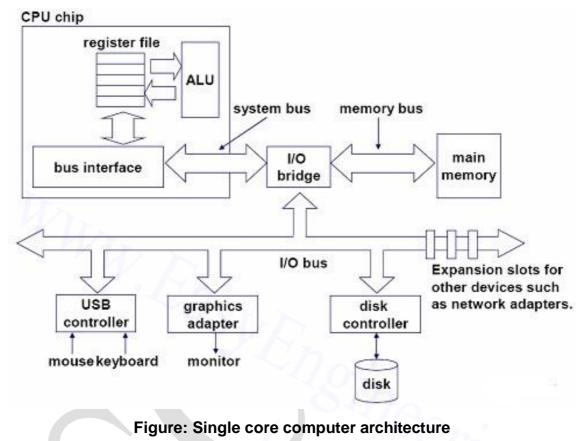

A computer consists of five functionally independent main parts. They are

- 1. Input

- 2. Memory

- 3. Arithmetic and logic

- 4. Output

- 5. Control unit

### Basic functional units of a computer

The computer accepts programs and the data through an input and stores them in the memory. The stored data are processed by the arithmetic and logic unit under program control. The processed data is delivered through the output unit. All above activities are directed by control unit.

### a. Input unit

The computer accepts coded information through input unit. The input can be from human operators, electromechanical devices such as keyboards or from other computer over communication lines.

**Examples of input devices are** Keyboard, joysticks, trackballs and mouse are used as graphic input devices in conjunction with display

### Keyboard

- It is a common input device.

- Whenever a key is pressed; the corresponding letter or digit is automatically translated into its corresponding binary code and transmitted over cable to the memory of the computer.

### Memory unit

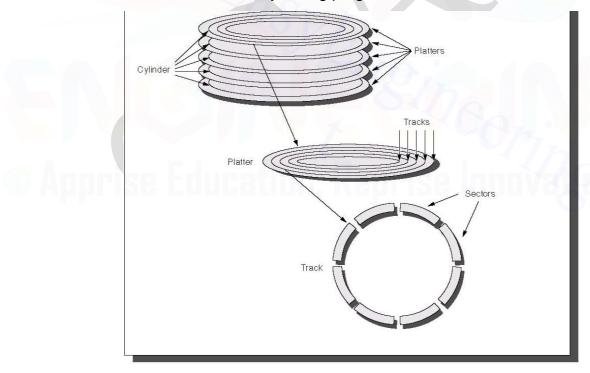

Memory unit is used to store programs as well as data. Memory is classified into primary and secondary storage.

### Primary storage

It also called main memory. It operates at high speed and it is expensive. It is made up of large number of semiconductor storage cells, each capable of storing one bit of information. These cells are grouped together in a fixed size called word. This facilitates reading and writing the content of one word (n bits) in single basic operation instead of reading and writing one bit for each operation.

### Secondary storage

It is slow in speed. It is cheaper than primary memory. Its capacity is high. It is used to store information that is not accessed frequently. Various secondary devices are magnetic tapes and disks, optical disks (CD-ROMs), floppy etc.

### Figure: The basic components of computer system

### b. Arithmetic and logic unit

Arithmetic and logic unit (ALU) and control unit together form a processor. Actual execution of most computer operations takes place in arithmetic and logic unit of the processor. Example: Suppose two numbers located in the memory are to be added. They are brought into the processor, and the actual addition is carried out by the ALU.

### **Registers:**

Registers are high speed storage elements available in the processor. Each register can store one word of data. When operands are brought into the processor for any operation, they are stored in the registers. Accessing data from register is faster than that of the memory.

### c. Output unit

The function of output unit is to produce processed result to the outside world in human understandable form. Examples of output devices are Graphical display, Printers such as inkjet, laser, dot matrix and so on. The laser printer works faster.

**Figure: Computer Components**

### d. Control unit

Control unit coordinates the operation of memory, arithmetic and logic unit, input unit, and output unit in some proper way. The **control unit** issues **control signals** that cause the CPU (and other components of the computer) to fetch the instruction to the IR (Instruction Register) and then execute the actions dictated by the machine language instruction that has been stored there. Control units are well defined, physically separate unit that interact with other parts of the machine.

A set of control lines carries the signals used for timing and synchronization of events in all units Example: Data transfers between the processor and the memory are controlled by the control unit through timing signals. **Timing signals** are the signals that determine when a given action is to take place.

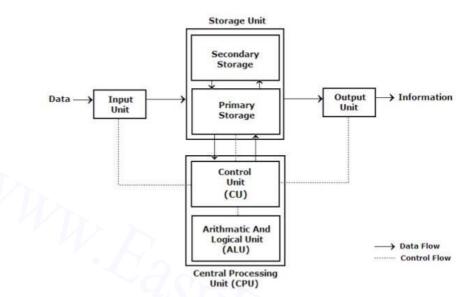

### **Basic Operational Concept**

Computer Components:

Top-Level view

PC the **program counter** contains the address of the assembly language instruction to be executed next. IR the **instruction register** contains the binary

word corresponding to the machine language version of the instruction currently being executed.

MAR the **memory address register** contains the address of the word in main memory that is being accessed. The word being addressed contains either data or a machine language instruction to be executed.

MBR the **memory buffer register** (also called MDR for memory data register) is the register used to communicate data to and from the memory.

The operation of a processor is characterized by a *fetch-decode-execute* cycle. In the first phase of the cycle, the processor fetches an instruction from memory. The address of the instruction to fetch is stored in an internal register named the *program counter*, or PC. As the processor is waiting for the memory to respond

with the instruction, it increments the PC. This means the fetch phase of the next cycle will fetch the instruction in the next sequential location in memory. In the decode phase the processor stores the information returned by the memory in another internal register, known as the instruction register, or IR. The IR now holds a single machine instruction, encoded as a binary number. The processor decodes the value in the IR in order to figure out which operations to perform in the next stage. In the execution stage the processor actually carries out the instruction. This step often requires further memory operations; for example, the instruction may direct the processor to fetch two operands from memory, add them, and store the result in a third location (the addresses of the operands and the result are also encoded as part of the instruction). At the end of this phase the machine starts the cycle

over again by entering the fetch phase for the next instruction. The CPU exchanges data with memory. For this purpose, it typically makes use of **two internal (to the CPU) register:**

- A memory address register (MAR), which specifies the address in memory for the next read or write, and

- A memory buffer register (MBR), which contains the data to be written into memory or receives the data read from memory.

An I/O addresses register (I/OAR) specifies a particular I/O device. An I/O buffer (I/OBR) register is used for the exchange of data between an I/O module and the CPU.A memory module consists of a set of locations, defined by sequentially numbered address. Each location contains a binary number that can be

15

interpreted as either an instruction or data. An I/O module transfers data from external devices to CPU and memory, and vice versa.

It contains internal buffers for temporarily holding these data until they can be sent on. Instructions can be classified as one of three major types: arithmetic/logic, data transfer, and control. Arithmetic and logic instructions apply primitive functions of one or two arguments, for example addition, multiplication, or logical AND.

# 2. State the CPU performance equation and discuss the factors that affect the performance of a computer. [R-2013]?[May/June 2014]

**Response time:** The time between the start and the completion of an event also referred to as *execution time*.

**Throughput:** The total amount of work done in a given time. In comparing design alternatives, we often want to relate the performance of two different machines, say X and Y. The machine X is faster than Y is used here to mean that the response time or execution time is lower on X than on Y for the given task. In particular, if X is *n* times faster than Y

$\frac{\text{Execution time}_{Y}}{\text{Execution time}_{X}} = n$

Since execution time is the reciprocal of performance, the following relationship

$$n = \frac{\text{Execution time}_{Y}}{\text{Execution time}_{X}} = \frac{\frac{1}{\text{Performance}_{Y}}}{\frac{1}{\text{Performance}_{X}}} = \frac{\text{Performance}_{X}}{\text{Performance}_{Y}}$$

The performance and execution time are reciprocals, increasing performance decreases execution time. To help avoid confusion between the terms Increasing and decreasing, we usually say improve performance or improve execution time when we mean increase performance and decrease execution time.

### **CPU** performance equation:

All computers are constructed using a clock running at a constant rate. These discrete time events are called ticks, clock ticks, clock periods, clocks, cycles, or clock cycles. Computer designers refer to the time of a clock period by its duration (e.g., 1 ns) or by its rate (e.g., 1 GHz). CPU time for a program can then be expressed two ways:

### CPU time = CPU clock cycles for a program x CPU time=CPU clock cycle to exe a pgm / clock rate

In addition to the number of clock cycles needed to execute a program, we can also count the number of instructions executed, the instruction path length or instruction count (IC).

CPI is computed as:

$$CPI = \frac{CPU \text{ clock cycles for a program}}{Instruction Count}$$

By transposing instruction count in the above formula, clock cycles can be defined As IC \* CPI. This allows us to use CPI in the execution time formula

CPU time = Instruction Count × Clock cycle time × Cycles per Instruction

CPU to calculate the number of total CPU clock cycles as,

CPU clock cycles =

$$\sum_{i=1}^{n} \text{IC}_{i} \times \text{CPI}_{i}$$

### Basic performance equation

Let T be the time required for the processor to execute a program in high level language. The compiler generates machine language object program corresponding to the source program. Assume that complete execution of the program requires the execution of N machine language instructions.

Assume that average number of basic steps needed to execute one machine instruction is S, where each basic step is completed in one clock cycle. If the clock rate is R cycles per second, the program execution time is given by  $T = (N \times S) / R$  this is often called Basic performance equation.

To achieve high performance, the performance parameter T should be reduced. T value can be reduced by reducing N and S, and increasing R.

- Value of N is reduced if the source program is compiled into fewer number of machine instructions.

- Value of S is reduced if instruction has a smaller no of basic steps to perform or if the execution of the instructions is overlapped.

- Value of R can be increased by using high frequency clock, ie. Time required to complete a basic execution step is reduced.

- N, S and R are dependent factors. Changing one may affect another.

### **Choosing Programs to Evaluate Performance**

There are five levels of programs used in such circumstances, listed below in decreasing order of accuracy of prediction.

**1. Real applications-**Real applications have input, output, and options that a user can select when running the program. There is one major downside to using real applications as benchmarks: Real applications often encounter portability problems arising from dependences on the operating system or compiler. Enhancing portability often means modifying the source and sometimes

eliminating some important activity, such as interactive graphics, which tends to be more system-dependent.**Modified (or scripted) applications**-In many cases, real applications are used as the building block for a benchmark either with modifications to the application or with a script that acts as stimulus to the application. Applications are modified for two primary reasons: to enhance portability or to focus on one particular aspect of system performance. For example, to create a CPU-oriented benchmark, I/O may be removed or restructured to minimize its impact on execution time. Scripts are used to reproduce interactive behavior, which might occur on a desktop system, or to simulate complex multiuser interaction, which occurs in a server system.

**2. Kernels-**Several attempts have been made to extract small, key pieces from real programs and use them to evaluate performance. Kernels are best used to isolate performance of individual features of a machine to explain the reasons for differences in performance of real programs.

**4. Toy benchmarks**-Toy benchmarks are typically between 10 and 100 lines of code and produce a result the user already knows before running the toy program. Programs like Sieve of Eratosthenes, Puzzle, and Quicksort are popular because they are small, easy to type, and run on almost any computer. The best use of such programs is beginning programming assignments.

**5. Synthetic benchmarks**- Synthetic benchmarks try to match the average frequency of operations and operands of a large set of programs. Whetstone and Dhrystone are the most popular synthetic benchmarks.

18

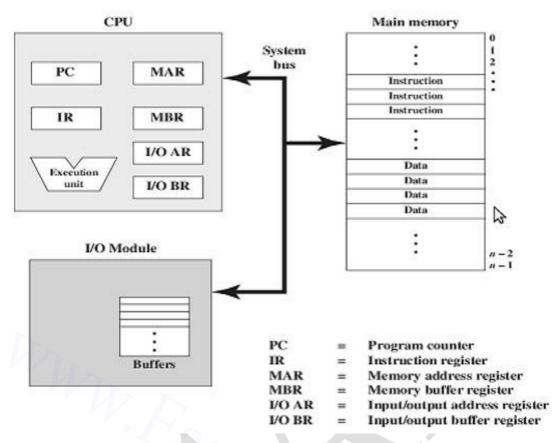

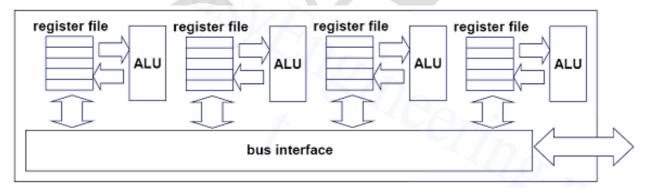

3. (i)Explain the need to switch from uniprocessors to multiprocessors and draw the performance chart for processors over years. [R-2013]?[May/June 2013]

- > Multicore microprocessors

- More than one processor per chip

- Requires explicitly parallel programming

- Compare with instruction level parallelism

- Hardware executes multiple instructions at once

- Hidden from the programmer

- Hard to do

- Programming for performance

- Load balancing

- Optimizing communication and synchronization

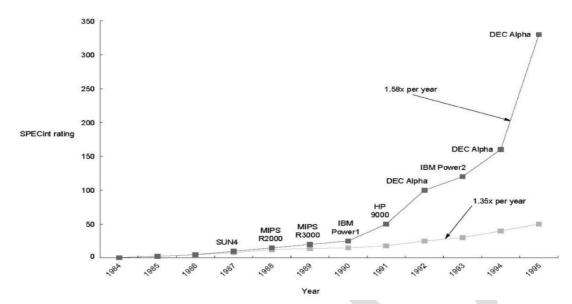

Figure Growth in processor performance since the mid-1980s

# (ii) Explain how clock rate and power are related to each other in microprocessor over years with a neat graph (or) Elaborate about power wall with neat sketch. [R-2013]

The dominant technology for integrated circuits is called CMOS (complementary metal oxide semiconductor). For CMOS, the primary source of energy consumption is so-called dynamic energy— that is, energy that is consumed when transistors switch states from 0 to 1 and vice versa. The dynamic energy depends on the capacitive loading of each transistor and the voltage applied.

### Energy $\propto$ Capacitive load $\times$ Voltage<sup>2</sup>

This equation is the energy of a pulse during the logic transition of  $0 \rightarrow 1 \rightarrow 0$  or  $1 \rightarrow 0 \rightarrow 1$ . The energy of a single transition is then

### Energy $\propto 1/2 \times Capacitive load \times Voltage^2$

The power required per transistor is just the product of energy of a transition and the frequency of transitions:

### Power $\propto 1/2 \times Capacitive load \times Voltage^2 \times Frequency switched$

Frequency switched is a function of the clock rate. The capacitive load per transistor is a function of both the number of transistors connected to an output (called the fanout) and the technology, which determines the capacitance of both wires and transistors.

### (iii) Explain the fundamentals of computer Design. [R-2013]

Computer technology has made incredible progress in the roughly from last 55 years. This rapid rate of improvement has come both from advances in the technology used to build computers and from innovation in computer design. During the first 25 years of electronic computers, both forces made a major contribution; but beginning in about 1970, computer designers became largely dependent upon integrated circuit technology. During the 1970s, performance continued to improve at about 25% to 30% per year for the mainframes and minicomputers that dominated the industry.

The late 1970s after invention of microprocessor the growth roughly increased 35% per year in performance. This growth rate, combined with the cost advantages of a mass-produced microprocessor, led to an increasing fraction of the computer business. In addition, two significant changes are observed in computer industry.

### Fig. Growth in microprocessor Performance since the mid 1980s has been substantially higher than in earlier years as shown by plotting SPECint performance.

- First, the virtual elimination of assembly language programming reduced the need for object-code compatibility.

- Second, the creation of standardized, vendor-independent operating systems, such as UNIX and its clone, Linux, lowered the cost and risk of bringing out a new architecture.

These changes made it possible to successfully develop a new set of architectures, called RISC (Reduced Instruction Set Computer) architectures. In the early 1980s. The RISC-based machines focused the attention of designers on

two critical performance techniques, the exploitation of instruction-level parallelism and the use of caches.

The combination of architectural and organizational enhancements has led to 20 years of sustained growth in performance at an annual rate of over 50%. Figure shows the effect of this difference in performance growth rates.

The effect of this dramatic growth rate has been twofold.

First, it has significantly enhanced the capability available to computer users.

For many applications, the highest performance microprocessors of today outperform the supercomputer of less than 10 years ago.

• Second, this dramatic rate of improvement has led to the dominance of microprocessor-based computers across the entire range of the computer design.

### 4 (i) Explain the trends in technologies for building computer over time. (or) Explain various Technology trends in computer industry. [R-2013]

The designer must be especially aware of rapidly occurring changes in implementation technology. The following Four implementation technologies changed the computer industry.

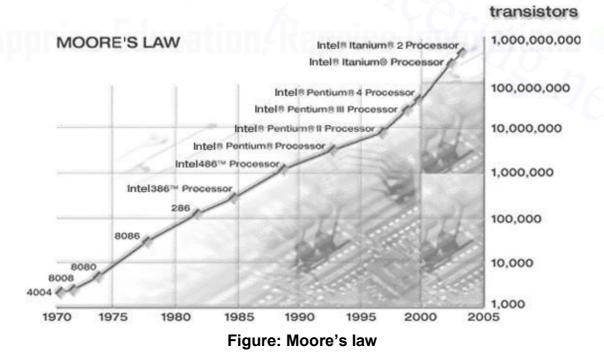

**1. Integrated circuit logic technology**: Transistor density increases by about 35% per year, and die size increases 10% to 20% per year. The combined effect is a growth rate in transistor count on a chip of about 55% per year.

**2. Semiconductor DRAM:** Density increases by between 40% and 60% per year and Cycle time has improved very slowly, decreasing by about one-third in 10 years. Bandwidth per chip increases about twice as fast as latency decreases. In addition, changes to the DRAM interface have also improved the bandwidth.

**3. Magnetic disk technology:** it is improving more than 100% per year. Prior to 1990, density increased by about 30% per year, doubling in three years. It appears that disk technology will continue the faster density growth rate for some time to come. Access time has improved one-third in 10 years.

4. Network Technology: Network Performance depends both on the performance of switches and on the performance of the transmission system, both latency and bandwidth can be improved, though recently bandwidth has been the primary focus. Scaling of Transistor Performance, Wires, and Power in Integrated Circuits Transistor Performance:

Integrated circuit processes are characterized by the feature size, which is decreased from 10 microns in 1971 to 0.18 microns in 2001. Since a transistor is a 2-dimensional object, the density of transistors increases quadratically with a linear decrease in feature size. The increase in transistor performance, this combination of scaling factors leads to a complex interrelationship between transistor performance and process feature size.

### Wires

The signal delay for a wire increases in proportion to the product of its resistance and capacitance. As feature size shrinks wires get shorter, but the resistance and capacitance per unit length gets worse. Since both resistance and capacitance depend on detailed aspects of the process, the geometry of a wire, the loading on a wire, and even the adjacency to other structures.

### Power

Power also provides challenges as devices are scaled. For modern CMOS microprocessors, the dominant energy consumption is in switching transistors. The energy required per transistor is proportional to the product of the load capacitance of the transistor, the frequency of switching, and the square of the voltage.

### Moore's Law

Gordon Moore (Founder of Intel) observed in 1965 that the number of transistors that could be crammed on a chip doubles every year.

Based on SPEED, the CPU has increased dramatically, but memory and disk have increased only a little. This has led to dramatic changed in architecture, Operating Systems, and Programming practices.

### Capacity

| Logic 2x in 3 years |  |

|---------------------|--|

| DRAM 4x in 3 years  |  |

| Disk 4x in 3 years  |  |

Speed (latency) 2x in 3 years 2x in 10 years 2x in 10 years

Electronics technology continues to evolve Increased capacity and performance Reduced cost

# (ii) Explain the trends in Cost, Price for building computer over time. (or) Explain the impact of Time, volume and commodification on Cost and Price. [R-2013]

- Price: selling a finished good

- > 1999: more than half the PCs sold were priced at less than \$1000

- Cost: the amount spent to produce it, including overhead

### The Impact of Time, Volume, Commodification:

- Time

- The cost of a manufactured computer component decreases over time even without major improvements in the basic implementation technology.

- The underlying principle that drives costs down is the learning curve manufacturing costs decrease over time.

- Yield: the percentage of the manufactured devices that survive the testing procedure.

As the technology matures over time, the yield improves and hence, things get cheaper.

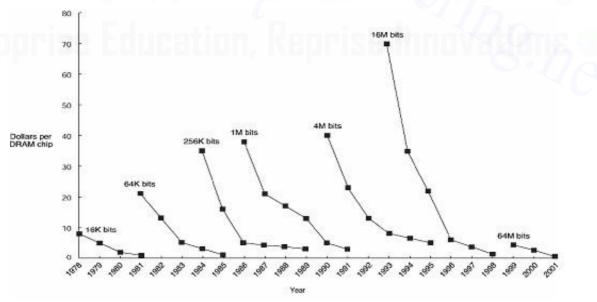

Prices of six generations of DRAMs

The following Figure plots the price of a new DRAM chip over its lifetime.

Between the start of a project and the shipping of a produce, say, two years, the cost of a new DRAM drops by a factor of between 5 and 10 in constant dollars.

> Price of an Intel Pentium III at a Given Frequency

It decreases over time as yield enhancements decrease the cost of a good die and competition forces price reductions.

➢ Wafer and Dies

Exponential cost decrease since silicon manufacture technology basically the same:

A wafer is tested and chopped into dies that are packaged

- Volume

- Volume is the second key factor in determining cost. Increasing volume affecting the cost in several ways.

- Increasing volume decreases cost (time for learning curve),

- Increases purchasing and manufacturing efficiency

- Commodities

- Commodities are Products are sold by multiple vendors in large volumes are essentially identical

- Virtually all the products sold on the shelves of grocery stores are commodities, as are standard DRAMs, disks, monitors, and keyboards.

- In the past 10 years, much of the low end of the computer business has become a commodity business focused on building IBM-compatible PCs.

- Improved competition leads to reduced cost

- Cost of an Integrated Circuit (IC)

The cost of packaged integrated circuit is

$Cost of IC = \frac{costof die + Costof testing die + Costof packaging and finaltest}{Finaltest yield}$

A greater portion of the cost that varies between machines.

# Diesperwafer =  $\frac{\pi x Waferradius^2}{DieArea} - \frac{\pi x Waferdiameter}{\sqrt{2}x DieArea}$

Number of Dies per wafer is sensitive to die size.

$Dieyield = Wafer yieldx (1 + (\frac{Defects perunitareax DieArea}{\alpha})^{-\alpha}$

In today's technology, a=4, Defects per unit area = 0.4 and 0.8 per cm<sup>2</sup>

5.(i) Suppose we have made the following measurements:

Frequency of FP operations (other than FPSQR) = 25% Average CPI of FP operations = 4.0 Average CPI of other instructions = 1.33 Frequency of FPSQR= 2% CPI of FPSQR = 20 Assume that the two design alternatives are to decrease the CPI of FPSQR to 2 or to decrease the average CPI of all FP operations to 2.5. Compare these two design alternatives using the CPU performance equation. [R-2013]

$$CPI_{original} = \sum_{i=1}^{n} CPI_i \times \left(\frac{IC_i}{Instruction \ count}\right)$$

$$= (4 \times 25\%) + (1.33 \times 75\%) = 2.0$$

$CPI_{with new FPSQR} = CPI_{original} - 2\% \times (CPI_{old FPSQR} - CPI_{of new FPSQR only})$  $= 2.0 - 2\% \times (20 - 2) = 1.64$

$CPI_{new FP} = (75\% \times 1.33) + (25\% \times 2.5) = 1.625$

$$Speedup_{new FP} = \frac{CPU \text{ time}_{original}}{CPU \text{ time}_{new FP}} = \frac{IC \times Clock \text{ cycle} \times CPI_{original}}{IC \times Clock \text{ cycle} \times CPI_{new FP}}$$

$$= \frac{CPI_{original}}{CPI_{new FP}} = \frac{2.00}{1.625} = 1.23$$

(ii)A program runs in 20 seconds on machine A with a clock speed of 200 MHz. A computer architect wants to build machine B, which will run this program in 6 seconds. The architect has determined that a substantial increase in the clock rate possible, but this will affect the design of the rest of the CPU, causing machine B to require 1.2 times as many clock cycle as machine A for this program. What clock rate should he target for a best design? [R-2013]

Solution:

$$CPU time for A = \frac{CPU clock cycles_A}{clock rate_A}$$

$$20 \text{ seconds} = \frac{\text{CPU clock cycles}_{\text{A}}}{200 \times 10^6 \frac{\text{cycles}}{\text{seconds}}}$$

$CPU \ clock \ cycle_A = 20 \ x \ 200 \ x \ 10^6 \ cycles$

### CPU time for B may be found as shown below

CPU time for B =  $\frac{1.2 \text{ x CPU clock cycles}_{A}}{\text{clock rate}_{B}}$ 6 seconds =  $\frac{1.2 \text{ x 4000 x 10}^{6} \text{ cycles}}{\text{clock rate}_{B}}$

$clock \ rate_{B} = \ \frac{1.2 \times 4000 \times 10^{6} \ cycles}{6 \ seconds} = 800 \times 10^{6} \frac{cycles}{seconds} = 800 \text{ MHz}$

Therefore ,Machine B must have four times the clock rate of A to run the program in 6 seconds

### UNIT II

### INSTRUCTION LEVEL PARALLELISM

### PART A

### 1. What is ILP? [Nov/Dec 2012][May/June 2012]

ILP = Instruction level parallelism

• Multiple operations (or instructions) can be executed in parallel

### 2. What are the needs of ILP? [R-2013]

- Sufficient resources

- Parallel scheduling

- Hardware solution

- Software solution

- Application should contain ILP

### 3. What are the various hazards?[May/June 2014] [April/May 2017]

Three types of hazards

1.Structural 2.Data dependence 3.Control dependence

### 4. What is dynamic scheduling? [May/June 2013](NOV/DEC 2016)

• *Dynamic scheduling*: hardware rearranges instruction execution to reduce stalls Allow instructions behind stall to proceed

### 5. What are the advantages of dynamic scheduling? (Apr/may 2017)

- Handles cases when dependences unknown at compile time

- e.g., because they may involve a memory reference

- It simplifies the compiler

- Allows code compiled for one machine to run efficiently on a different machine, with different number of function units (FUs), and different pipelining

### 6. What is branch prediction? [May/June 2013]

- High branch penalties in pipelined processors:

- With on average 20% of the instructions being a branch, the maximum ILP is five

- CPI = CPIbase + fbranch \* fmisspredict \* penalty

- Large impact if:

- Penalty high: long pipeline

- CPIbase low: for multiple-issue processors

### 7. What is speculation? [May/June 2012]

Hardware-based speculation follows the predicted flow of data values to choose when to execute instructions. This method of executing programs is essentially a *data flow execution:* Operations execute as soon as their operands are available.

### 8. What are the four steps involved in instruction execution? [R-2013]

1.Issue 2. Execute 3.Write result 4.Commit

### 9. How to calculate the value of CPI. [R-2013]

The value of the CPI (cycles per instruction) for a pipelined processor is the sum of the base CPI and all contributions from stalls: Pipeline CPI = Ideal pipeline CPI+Structuralstalls+Data hazard stalls + Control stalls

### 10. What is ideal pipeline CPI? [Nov/Dec 2013]

The *ideal pipeline CPI* is a measure of the maximum performance attainable by the implementation. By reducing each of the terms of the right-hand side, we minimize the overall pipeline CPI or, alternatively, increase the IPC (instructions per clock).

### 11. What are the types of data dependencies?

### [April/May 2015] (NOV/DEC 2016)

There are three different types of dependences: *data dependences* (also called true data dependences), *name dependences*, and *control dependences*.

### 12. What is instruction commit? [R-2013]

When an instruction is no longer speculative, we allow it to update the register file or memory; we call this additional step in the instruction execution sequence *instruction commit.*

### 13. What is reorder buffer? [R-2013]

Instruction execution sequence requires an additional set of hardware buffers that hold the results of instructions that have finished execution but have not committed. This hardware buffer is called the *reorder buffer*.

### 14. What is control speculation? [R-2013]

Loads incur high latency

- Need to schedule loads as early as possible

- Two barriers branches and stores

Control speculation – move loads above branches

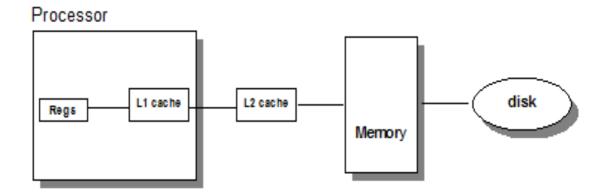

### 15. What is principle of locality? [Nov/Dec 2016]

An implication of locality is that we can predict with reasonable accuracy what instructions and data a program will use in the near future based on its accesses in the recent past. The principle of locality also applies to data accesses, though not as strongly as to code accesses.

### PART B

### 1. (i)What is multithreading and explain the approaches of multithreading. [May/Jun 2014], [Apr/ May 2015]

Multithreading allows multiple threads to share the functional units of a single processor in an overlapping fashion. To permit this sharing, the processor must duplicate the independent state of each thread. For example, a separate copy of the register file, a separate PC, and a separate page table are required for each thread. **Software and hardware multithreading**

- A "hardware thread" is a physical CPU or core. So, a 4 core CPU can support 4 hardware threads at once - the CPU really is doing 4 things at the same time.

- One hardware thread can run many software threads. In modern operating systems, this is often done by time-slicing each thread gets a few milliseconds to execute before the OS schedules another thread to run on that CPU. Since the OS switches back and forth between the threads quickly, it appears as if one CPU is doing more than one thing at once, but in reality, a core is still running only one hardware thread, which switches between many software threads.

- Modern JVMs map java threads directly to the native threads provided by the OS, so there is no inherent overhead introduced by java threads vs native threads. As to hardware threads, the OS tries to map threads to cores, if there are sufficient cores. So, if you have a java program that starts

4 threads, and have more 4 or more cores, there's a good chance your 4

4 threads, and have more 4 or more cores, there's a good chance your 4 threads will run truly in parallel on 4 separate cores, if the cores are idle.

- Multithreading computers have hardware support to efficiently execute multiple threads. These are distinguished from multiprocessing systems (such as multi-core systems) in that the threads have to share the resources of a single core: the computing units, the CPU caches and the translation look aside buffer (TLB).

- Where multiprocessing systems include multiple complete processing units, multithreading aims to increase utilization of a single core by leveraging thread-level as well as instruction-level parallelism. As the two techniques

are complementary, they are sometimes combined in systems with multiple multithreading CPUs and in CPUs with multiple multithreading cores.

### There are two main approaches to multithreading.

### Cycle-by-cycle interleaving (Fine Grained Multithreading)

*Fine-grained multithreading* switches between threads on each instruction, causing the execution of multiples threads to be interleaved. This interleaving is often done in a round-robin fashion, skipping any threads that are stalled at that time.

The next instruction of a thread is fed into the pipeline after the retirement of the previous instruction. This eliminates the need for forwarding data paths, but implies that there must be as many threads as pipeline stages. This can be a problem for contemporary super pipelined processors. Furthermore, in order to fully hide the memory latency, the number of threads must be larger than the memory latency in cycles.

### Block interleaving (Coarse Grained Multithreading)

**Coarse-grained multithreading**was invented as an alternative to fine-grained multithreading. A coarse-grained multithreading switches thread only on costly stalls, such as level two caches misses.

It is also called as block interleaving; the processor starts executing another thread if the current thread experiences an event that is predicted to have a significantly long latency. If it can be predicted that the latency is larger than the cost of a thread switch, then the processor can at least hide part of the latency by executing another thread.

**Simultaneous Multithreading**: Converting Thread-Level Parallelism into Instruction-Level Parallelism:

Simultaneous multithreading (SMT) is a variation on multithreading that uses the resources of a multiple issue, dynamically-scheduled processor to exploit TLP at the same time it exploits ILP. The key insight that motivates SMT is that modern multiple-issue processors often have more functional unit parallelism available than a single thread can effectively use. Furthermore, with register renaming and dynamic scheduling, multiple instructions from independent threads can be issued without regard to the dependences among them; the resolution of the dependences can be handled by the dynamic scheduling capability.

- Simultaneous multithreading (SMT) tries to eliminate horizontalwaste(unused instruction slots in a cycle) because it fetches and issues instructions from different threads simultaneously.

- SMT is designed for superscalar processors, however. To implement this technique in a VLIW processor, several VLIW instructions have to be combined at runtime. This can be very difficult and may increase the cycle time because resource conflicts may occur since not every operation can be placed in each instruction slot. a bit needs to be added to every VLIW instruction to indicate that it can be issued across multiple cycles without violating dependencies.

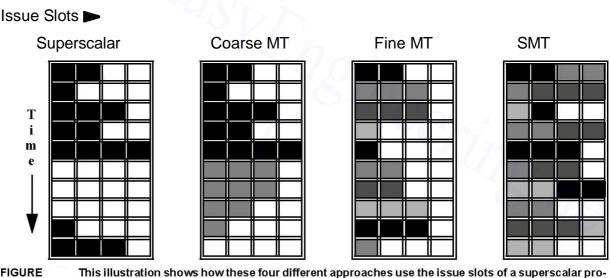

Figure illustrates the differences in a processor's ability to exploit the resources of a superscalar for the following processor configurations:

- n a superscalar with no multithreading support,

- n a superscalar with coarse-grained multithreading,

- n a superscalar with fine-grained multithreading, and

- n a superscalar with simultaneous multithreading.

FIGURE This illustration shows how these four different approaches use the issue slots of a superscalar processor. The horizontal dimension represents the instruction issue capability in each clock cycle. The vertical dimension represents a sequence of clock cycles. An empty (white) box indicates that the corresponding issue slot is unused in that clock cycle. The shades of grey and black correspond to four different threads in the multithreading processors. Black is also used to indicate the occupied issue slots in the case of the superscalar without multithreading support.

In the superscalar without multithreading support, the use of issue slots is limited

by a lack of ILP.

### Hardware Multithreading Techniques

Basically, three different hardware multithreading techniques can be distinguished:

- cycle-by-cycle interleaving (Fine Grained Multithreading)

- block interleaving (Coarse Grain Multithreading)

Simultaneous multithreading. (SMT)

In the coarse-grained multithreaded superscalar, the long stalls are partially hidden by switching to another thread that uses the resources of the processor.

In the fine-grained case, the interleaving of threads eliminates fully empty slots. Because only one thread issues instructions in a given clock cycle.

In the SMT case, thread-level parallelism (TLP) and instruction-level parallelism (ILP) are exploited simultaneously; with multiple threads using the issue slots in a single clock cycle.

### (ii)Compare hardware and software speculation mechanisms.

| Hardware Speculation                                                                                                                                                                                 | Software Speculation                                                                                                                                                                |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| Dynamic runtime disambiguation of memory addresses is<br>done using Tomasulo's algorithm. This disambiguation<br>allows us to move loads past stores at runtime.                                     | Dynamic runtime disambiguation of<br>memory addresses is difficult to do at<br>compile time for integer programs that<br>contain pointers                                           |  |  |

| Hardware-based speculation works better when control flow<br>is unpredictable, and when hardware-based branch prediction<br>is superior to software-based branch prediction done at<br>compile time. | Hardware-based branch prediction is<br>superior than software-based branch<br>prediction done at compile time.                                                                      |  |  |

| Hardware-based speculation maintains a completely precise exception model even for speculated instructions                                                                                           | Software-based approaches have added special support to allow this as well.                                                                                                         |  |  |

| Hardware-based speculation does not require compensation or bookkeeping code.                                                                                                                        | Software-based speculation require compensation or Bookkeeping                                                                                                                      |  |  |

| The ability to see further in the code is very poor in Hardware based speculation                                                                                                                    | Compiler-based approaches may benefit<br>from the ability to see further in the code<br>sequence, resulting in better code<br>scheduling than a purely hardware-driven<br>approach. |  |  |

| Hardware-based speculation with dynamic scheduling does<br>not require different code sequences to achieve good<br>performance                                                                       | Software-based speculation with dynamic<br>scheduling require different code sequences<br>to achieve good performance                                                               |  |  |

| Speculation in hardware is complex and requires additional hardware resources                                                                                                                        | Speculation in Software is Simple                                                                                                                                                   |  |  |

2. Explain hardware based speculation to overcome the control dependencies. [Apr/ May 2015], [Nov/ Dec 2014], [May/Jun 2013]

Hardware-based speculation combines three key ideas:

- Dynamic branch prediction to choose which instructions to execute

- Speculation to allow the execution of instructions before the control dependences are resolved (with the ability to undo the effects of an incorrectly speculated sequence)

• Dynamic scheduling to deal with the scheduling of different combinations of basic blocks.

Hardware-based speculation follows the predicted flow of data values to choose when to execute instructions. This method of executing programs is essentially a data flow execution: Operations execute as soon as their operands are available.

### Role of commit stage:

Using the bypassed value is like performing a speculative register read, since we do not know whether the instruction providing the source register value is providing the correct result until the instruction is no longer speculative. When an instruction is no longer speculative, we allow it to update the register file or memory we call this additional step in the instruction execution sequence instruction *commit.*

### **KEY IDEA BEHIND HARDWARE SPECULATION:**

- The key idea behind implementing speculation is to allow instructions to execute out of order but to force them to commit in order and to prevent any irrevocable action (such as updating state or taking an exception) until an instruction commits.

- Hence, when we add speculation, we need to separate the process of completing execution from instruction commit, since instructions may finish execution considerably before they are ready to commit. Adding this commit phase to the instruction execution sequence requires an additional set of hardware buffers that hold the results of instructions that have finished execution but have not committed. This hardware buffer, which we call the reorder buffer, is also used to pass results among instructions that may be speculated.

### ROLE OF RE-ORDER BUFFER:

The reorder buffer (ROB) provides additional registers in the same way as the reservation stations in Tomasulo's algorithm extend the register set. The ROB holds the result of an instruction between the times the operation associated with the instruction completes and the time the instruction commits. Hence, the ROB is a source of operands for instructions, just as the reservation stations provide operands in Tomasulo's algorithm.

- The key difference is that in Tomasulo's algorithm, once an instruction writes its result, any subsequently issued instructions will find the result in the register file.

- With speculation, the register file is not updated until the instruction commits (and we know definitively that the instruction should execute); thus, the ROB supplies operands in the interval between completion of instruction execution and instruction commit.

Each entry in the ROB contains four fields:

- Instruction type

- The instruction type field indicates whether the instruction is a branch (and has no destination result), a store (which has a memory address destination), or a register operation (ALU operation or load, which has register destinations).

- Destination field

- The destination field supplies the register number (for loads and ALU operations) or the memory address (for stores) where the instruction result should be written.

- Value field

- The value field is used to hold the value of the instruction result until the instruction commits.

- Ready field.

- The ready field indicates that the instruction has completed execution, and the value is ready.

### Here are the four steps involved in instruction execution:

1. **Issue**—Get an instruction from the instruction queue. Issue the instruction if there is an empty reservation station and an empty slot in the ROB; send the operands to the reservation station if they are available in either the registers or the ROB. Update the control entries to indicate the buffers are in use. The number of the ROB entry allocated for the result is also sent to the reservation station, so that the number can be used to tag the result when it is placed on the CDB. If either all reservations are full or the ROB is full, then instruction issue is stalled until both have available entries.

2. **Execute**—If one or more of the operands is not yet available, monitor the CDB while waiting for the register to be computed. This step checks for RAW hazards.

When both operands are available at a reservation station, execute the operation. Instructions may take multiple clock cycles in this stage, and loads still require two steps in this stage. Stores need only have the base register available at this step, since execution for a store at this point is only effective address calculation.

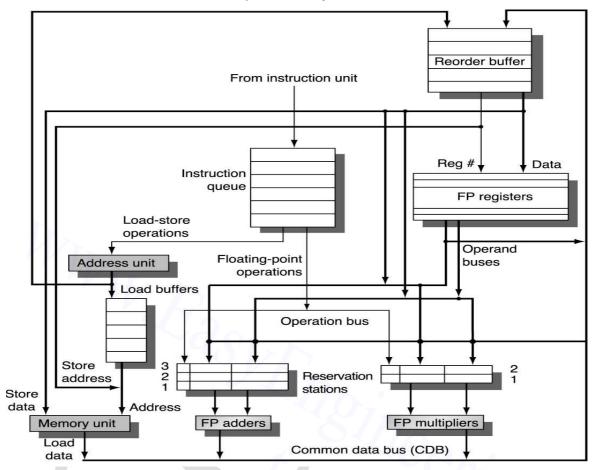

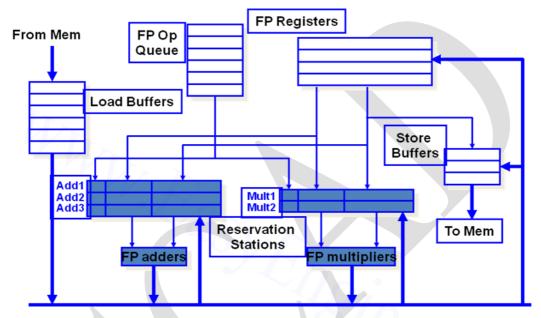

Figure: The basic structure of a MIPS floating-point unit using Tomasulo's algorithm.

3. Write result—When the result is available, write it on the CDB (with the ROB tag sent when the instruction issued) and from the CDB into the ROB, as well as to any reservation stations waiting for this result. Mark the reservation station as available. Special actions are required for store instructions. If the value to be stored is available, it is written into the Value field of the ROB entry for the store. If the value to be stored to be stored is not available yet, the CDB must be monitored until that value is broadcast, at which time the Value field of the ROB entry of the store is updated. For simplicity we assume that this occurs during the Write Results stage of a store; we discuss relaxing this requirement later.

4. **Commit**—this is the final stage of completing an instruction, after which only its result remains. (Some processors call this commit phase "completion" or

"graduation.") There are three different sequences of actions at commit depending on whether the committing instruction is a branch with an incorrect prediction, a store, or any other instruction (normal commit).

- The normal commit case occurs when an instruction reaches the head of the ROB and its result is present in the buffer; at this point, the processor updates the register with the result and removes the instruction from the ROB.

- When a branch with incorrect prediction reaches the head of the ROB, it indicates that the speculation was wrong. The ROB is flushed and execution is restarted at the correct successor of the branch. If the branch was correctly predicted, the branch is finished.

### 3. i)Describe the basic compiler techniques for exploiting Instruction Level Parallelism (ILP). [Apr/ May 2015], [Nov/ Dec 2014], [May/Jun 2013], [May/Jun 2014]

#### **Basic Pipeline Scheduling and Loop Unrolling**

- To keep a pipeline full, parallelism among instructions must be exploited by finding sequences of unrelated instructions that can be overlapped in the pipeline.

- To avoid a pipeline stall, a dependent instruction must be separated from the source instruction by a distance in clock cycles equal to the pipeline latency of that source instruction.

- Consider the following code segment, which adds a scalar to a vector:

for (i = 1000; i>0; i =i-1)

$$x[i] = x[i] + s;$$

We can see that this loop is parallel by noticing that the body of each iteration is independent. First, let's look at the performance of this loop, showing how we can use the parallelism to improve its performance for a MIPS pipeline with the latencies shown above.

| Instruction producing result | Instruction using result |   | Latency | in |

|------------------------------|--------------------------|---|---------|----|

| clock cycles                 |                          |   |         |    |

| FP ALU op                    | Another FP ALU op        | 3 |         |    |

| FP ALU op                    | Store double             | 2 |         |    |

| Load double                  | FP ALU op                | 1 |         |    |

|                              |                          |   |         |    |

Load double Store double 0 The first step is to translate the above segment to MIPS assembly language. In the following code segment, RI is initially the address of the element in the array with the highest address, and F2 contains the scalar value s. Register R2 is precompiled, so that 8(R2) is the address of the last element to operate on. The straightforward MIPS code, not scheduled for the pipeline, looks like this:

| Loop:  | L.D FO, O(R1) | ;F0=array |

|--------|---------------|-----------|

| elemen | t             |           |

| ADD.D F4, F0, F2 | ; add scalar in F2 |

|------------------|--------------------|

| S.D F4,0(R1)     | ;store result      |

| DADDUI RI,RI,#-8 | ;decrement pointer |

also be used to improve scheduling. Because it eliminates the branch, it allows instructions from different iterations to be scheduled together.

In this case, we can eliminate the data use stalls by creating additional independent instructions within the loop body. If we simply replicated the instructions when we unrolled the loop, the resulting use of the same registers could prevent us from effectively scheduling the loop. Thus, we will want to use different registers for each iteration, increasing the required number of registers.

The gain from scheduling on the unrolled loop is even larger than on the original loop. This increase arises because unrolling the loop exposes more computation that can be scheduled to minimize the stalls; the code above has no stalls.

39

Scheduling the loop in this fashion necessitates realizing that the loads and stores are independent and can be interchanged.

Without any scheduling the loop will execute as follows:

|       |       | Clock         | cycle i | ssued |

|-------|-------|---------------|---------|-------|

| Loop: | L.D   | F0,0(R1)      | 1       |       |

| stall |       |               | 2       |       |

|       | ADD.[ | D F4,F0,F2    | 3       |       |

| stall |       |               | 4       |       |

| stall |       |               | 5       |       |

|       | S.D F | 4,0(R1)       |         | 6     |

|       | DADD  | 0UI R1,R1,#-8 | 7       |       |

| stall |       |               | 8       |       |

|       | BNE F | R1,R2,Loop    | 9       |       |

| stall |       |               | 10      |       |

This code requires 10 clock cycles per iteration. We can schedule the loop to obtain only one stall:

```

Loop: L.D F0,0(R1)

DADDUI R1,R1,#-8

ADD.D F4,F0,F2

stall

BNE R1,R2,Loop ; delayed branch

S.D F4,8(R1) ; altered & interchanged with DADDUI

```

Execution time has been reduced from 10 clock cycles to 6. The stall after ADD.D is for the use by the S.D.

#### WITH UNROLLING:

```

Loop: L.D F0,0(R1)

L.D F6,-8(R1)

L.D F10,-16(R1)

L.D F14,-24(R1)

ADD.D F4,F0,F2

ADD.D F8,F6,F2

ADD.D F12,F10,F2

ADD.D F16,F14,F2

```

S.D F4,0(R1) S.D F8,-8(R1) DADDUI R1,R1,#-32 S.D F12,16(R1) BNE R1,R2,Loop S.D F16,8(R1) ;8-32 = -24

# ii) Explain the various dynamic branch prediction schemes. [Nov/ Dec 2014],[May/Jun 2013]

#### **Dynamic Branch Prediction and Branch-Prediction Buffers**

The simplest dynamic branch-prediction scheme is a branch-prediction buffer or *branch history table*. A *branch-prediction buffer is a small memory indexed* by the lower portion of the address of the branch instruction. The memory contains a bit that says whether the branch was recently taken or not. This scheme is the simplest sort of buffer; it has no tags and is useful only to reduce the branch delay when it is longer than the time to compute the possible target PCs. With such a buffer, we don't know, in fact, if the prediction is correct—it may have been put there by another branch that has the same low-order address bits.

• But this doesn't matter. The prediction is a hint that is assumed to be correct, and fetching begins in the predicted direction. If the hint turns out to be wrong, the prediction bit is inverted and stored back.

This simple 1-bit prediction scheme ---- has a performance shortcoming: Even if a branch is almost always taken, we will likely predict incorrectly twice, rather than once, when it is not taken, since the misprediction causes the prediction bit to be flipped.

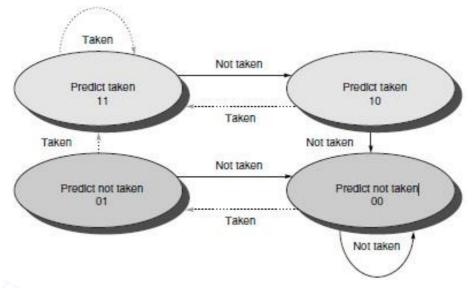

To remedy this weakness, 2-bit prediction schemes are often used. In a **2-bit scheme**, a prediction must miss twice before it is changed. Figure shows the finite-state processor for a 2-bit prediction scheme.

A branch-prediction buffer can be implemented as a small, special "cache" accessed with the instruction address during the IF pipe stage, or as a pair of bits attached to each block in the instruction cache and fetched with the instruction. If the instruction is decoded as a branch and if the branch is predicted as taken, fetching begins from the target as soon as the PC is known. Otherwise, sequential fetching and executing continue., if the prediction turns out to be wrong, the prediction bits are changed.

#### **Correlating Branch Predictors**

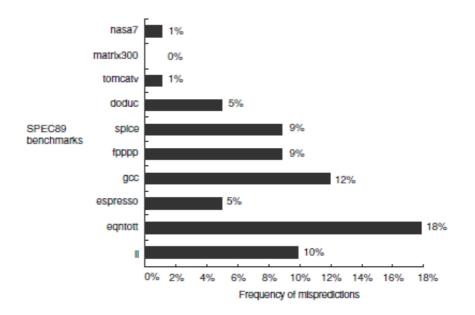

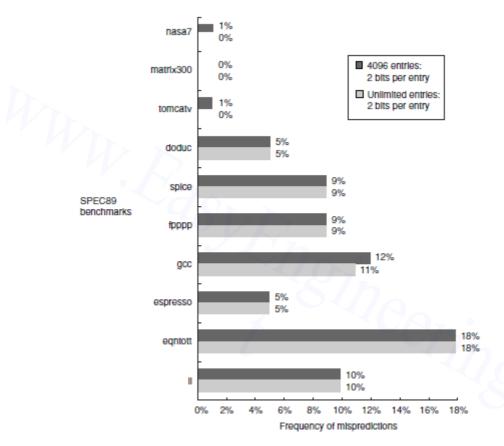

The 2-bit predictor schemes use only the recent behavior of a single branch to predict the future behavior of that branch. It may be possible to improve the prediction accuracy if we also look at the recent behavior of other branches rather than just the branch we are trying to predict. Consider a small code fragment from the equtott benchmark, a member of early SPEC benchmark suites that displayed particularly bad branch prediction behavior:

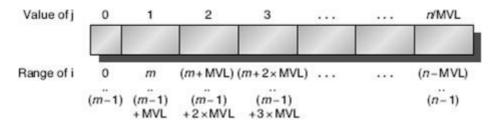

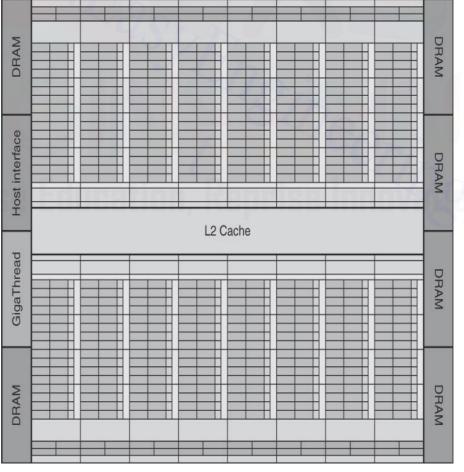

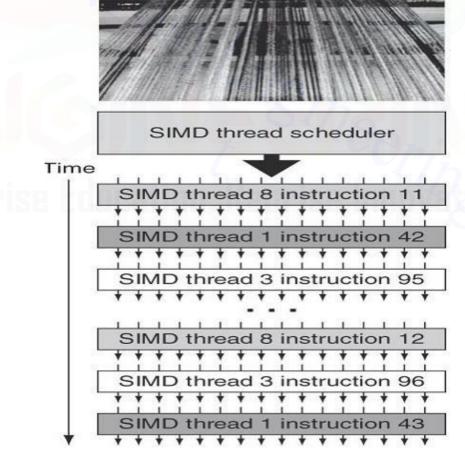

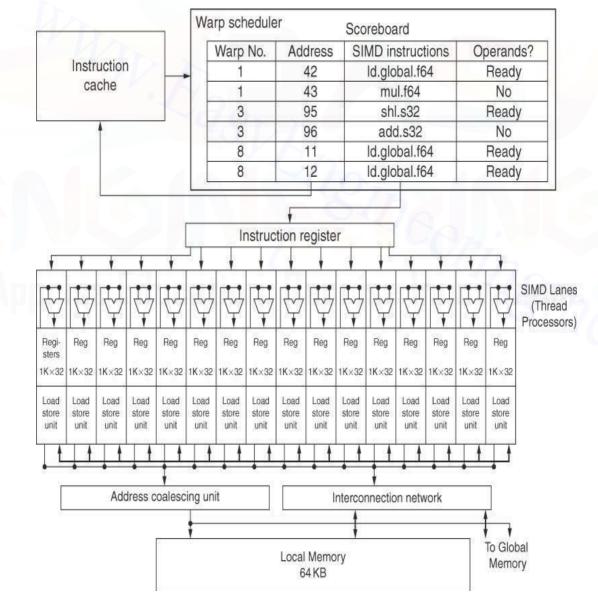

- Branch predictors that use the behavior of other branches to make a prediction are called correlating predictors or two-level predictors.